## **Refine Search**

## Search Results -

**Search History**

## DATE: Friday, May 26, 2006 Printable Copy Create Case

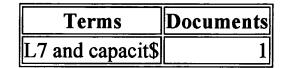

| <u>Set</u><br><u>Name</u> <u>Query</u><br>side by<br>side | <u>Hit</u><br><u>Count</u><br>result<br>set |

|-----------------------------------------------------------|---------------------------------------------|

| DB=PGPB; THES=ASSIGNEE; PLUR=YES; OP=OR                   |                                             |

| L21 L7 and capacit\$                                      | 1 <u>L21</u>                                |

| DB=USPT; THES=ASSIGNEE; PLUR=YES; OP=OR                   |                                             |

| L20 L18 and fet\$                                         | 1 <u>L20</u>                                |

| <u>L19</u> L18 and fet\$                                  | 1 <u>L19</u>                                |

| <u>L18</u> 5261694.pn.                                    | 1 <u>L18</u>                                |

| <u>L17</u> US-5666065-A.did.                              | 1 <u>L17</u>                                |

| DB=        | PGPB,USPT,USOC,EPAB,JPAB,DWPI,TDBD;                                                            |    |            |

|------------|------------------------------------------------------------------------------------------------|----|------------|

| THES=      | ASSIGNEE; PLUR=YES; OP=OR                                                                      |    |            |

| <u>L16</u> | L15 and FET\$                                                                                  | 7  | <u>L16</u> |

| <u>L15</u> | restraint\$ and (vehicle or automobile or car or flight or airplane) and (fir\$ near2 circuit) | 46 | <u>L15</u> |

| DB =       | USPT; THES=ASSIGNEE; PLUR=YES; OP=OR                                                           |    |            |

| <u>L14</u> | 5430314.pn.                                                                                    | 1  | <u>L14</u> |

| DB =       | PGPB; THES=ASSIGNEE; PLUR=YES; OP=OR                                                           |    |            |

| <u>L13</u> | 17 and restraint\$                                                                             | 1  | <u>L13</u> |

| <u>L12</u> | 20020121810                                                                                    | 1  | <u>L12</u> |

| DB =       | USPT; THES=ASSIGNEE; PLUR=YES; OP=OR                                                           |    |            |

| <u>L11</u> | 20020121810                                                                                    | 0  | <u>L11</u> |

| <u>L10</u> | 6878996.pn.                                                                                    | 1  | <u>L10</u> |

| DB =       | PGPB; THES=ASSIGNEE; PLUR=YES; OP=OR                                                           |    |            |

| <u>L9</u>  | L7 and 11                                                                                      | 1  | <u>L9</u>  |

| <u>L8</u>  | L7 and supply\$                                                                                | 1  | <u>L8</u>  |

| <u>L7</u>  | 20040108698                                                                                    | 1  | <u>L7</u>  |

| DB =       | PGPB, USPT, USOC, EPAB, JPAB, DWPI, TDBD;                                                      |    |            |

| THES=      | ASSIGNEE; PLUR=YES; OP=OR                                                                      |    |            |

| <u>L6</u>  | L5 and (vehicle or automobile or car or flight or airplane)                                    | 0  | <u>L6</u>  |

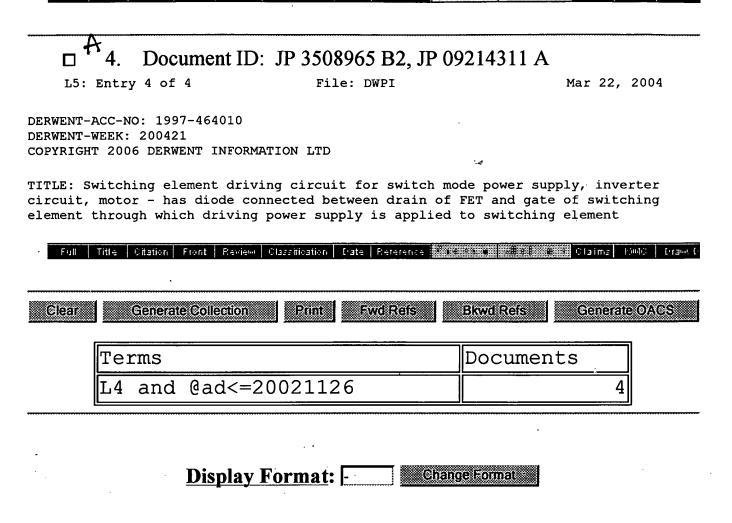

| <u>L5</u>  | L4 and @ad<=20021126                                                                           | 4  | <u>L5</u>  |

| <u>L4</u>  | 12 or L3                                                                                       | 10 | <u>L4</u>  |

| <u>L3</u>  | "reverse diode" and "N-channel FET"                                                            | 6  | <u>L3</u>  |

| <u>L2</u>  | "reverse diode" and "N-type FET"                                                               | 4  | <u>L2</u>  |

| DB =       | USPT; THES=ASSIGNEE; PLUR=YES; OP=OR                                                           |    |            |

| <u>L1</u>  | 6142130.pn.                                                                                    | 1  | <u>L1</u>  |

|            |                                                                                                |    |            |

## END OF SEARCH HISTORY

•

•

J

## First HitPrevious DocNext DocGo to Doc#End of Result Set

Generate Collection Print

L16: Entry 7 of 7

File: DWPI

Clear

Dec 16, 1992

DERWENT-ACC-NO: 1992-417372 DERWENT-WEEK: 199952 COPYRIGHT 2006 DERWENT INFORMATION LTD

TITLE: <u>Vehicle</u> passenger <u>restraint</u> firing circuit – uses microprocessor to control operation with diagnostic ASIC monitoring crash sensor to bias safer sensor and replace inoperable <u>FET</u> under failure conditions

INVENTOR: MUSSER, K E; PAYE, J R ; WHITE, C W

PATENT-ASSIGNEE: AUTOMOTIVE SYSTEMS LAB INC (AUTON)

PRIORITY-DATA: 1991US-0715344 (June 14, 1991)

Search Selected Search ALL

PATENT-FAMILY:

| PUB-NO               | PUB-DATE          | LANGUAGE | PAGES | MAIN-IPC   |

|----------------------|-------------------|----------|-------|------------|

| EP 518501 A1         | December 16, 1992 | E        | 007   | B60R021/00 |

| <u>KR 126667 B1</u>  | December 26, 1997 |          | 000   | B60R021/16 |

| AU 9218036 A         | December 24, 1992 |          | 000   | B60R021/32 |

| <u>CA 2069214 A</u>  | December 15, 1992 |          | 000   | B60R021/32 |

| <u>US 5261694 A</u>  | November 16, 1993 |          | 006   | B60R021/16 |

| <u>EP 518501 B1</u>  | March 20, 1996    | Е        | 009   | B60R021/00 |

| <u>DE 69209151 E</u> | April 25, 1996    |          | 000   | B60R021/00 |

| <u>CA 2069214 C</u>  | December 17, 1996 |          | 000   | B60R021/32 |

DESIGNATED-STATES: DE ES FR GB IT DE ES FR GB IT

CITED-DOCUMENTS:1.Jnl.Ref; EP 305656 ; US 4958851 ; US 5083276 ; US 5085464 ; 01Jnl.Ref

#### APPLICATION-DATA:

| PUB-NO      | APPL-DATE     | APPL-NO        | DESCRIPTOR |

|-------------|---------------|----------------|------------|

| EP 518501A1 | May 19, 1992  | 1992EP-0304499 |            |

| KR 126667B1 | June 12, 1992 | 1992KR-0010227 |            |

| AU 9218036A | June 5, 1992  | 1992AU-0018036 |            |

| CA 2069214A | May 22, 1992  | 1992CA-2069214 |            |

| US 5261694A | June 14, 1991 | 1991US-0715344 |            |

| EP 518501B1  | May 19, 1992 | 1992EP-0304499 |          |

|--------------|--------------|----------------|----------|

| DE 69209151E | May 19, 1992 | 1992DE-0609151 |          |

| DE 69209151E | May 19, 1992 | 1992EP-0304499 |          |

| DE 69209151E |              | EP 518501      | Based on |

| CA 2069214C  | May 22, 1992 | 1992CA-2069214 |          |

INT-CL (IPC): B60R 21/00; B60R 21/16; B60R 21/32

ABSTRACTED-PUB-NO: EP 518501A BASIC-ABSTRACT:

The circuit has a relatively-low-threshold acceleration-responsive switch (14) of an acceleration sensor (safing sensor) (16) in series with parallel firing legs (18a,18b) each having in series an explosive squib (20) and a <u>FET</u> (22), all operating under the control of a microprocessor (24) which responds to the output from an electronic crash sensor (16).

A Diagnostic ASIC (44) under the control of the microprocessor monitors the performance of the crash sensor and on detection of a failure applies a current to the safer integral test coil (38) to bias the switch contacts away from operation. The microprocessor the turns on another <u>FET</u> (46) to pull down to ground one side of the squib to replace the inoperable <u>FET</u>.

ADVANTAGE - Provides circuit with two sensors in series for improved reliability and includes maintaining operation under single sensor failure conditions.

ABSTRACTED-PUB-NO: EP 518501B EQUIVALENT-ABSTRACTS:

A control circuit for actuating a safety restraint in a motor vehicle comprising: a firing path (12,18) having in series a first normally-open switch means (14,16) for closing in response to vehicle therefore, a current-responsive trigger means (20) for actuating said safety restraint, and a second normally-open switch means (22) for closing in response to a second threshold value higher than said first threshold value; means (28) for applying a voltage across said firing path; failure detecting means (44) for detecting a failure of said first switch means (14,16) and/or said second switch means (22); threshold-adjusting means (36,38) responsive to said failure detecting means (44) for increasing the threshold value of said first switch means (14,16), wherein said threshold-adjusting means (36,38) operates to increase the threshold value of said first switch means (14,16) upon detection of a failure of said second switch means (22); shunt means (46), responsive to said failure detecting means (44) and operation of said threshold-adjusting means (36,38), for shunting said second switch means (22), wherein said shunt means (46) operates to shunt said second switch means (22) after operation of said thresholdadjusting means (36,38) upon a detection of a failure of said second switch means (22); characterised in that said control circuit further comprises: sensor means (26) for generating a first signal representative of instantaneous vehicle acceleration; processor means (24) responsive to said first signal for generating a second signal when said first signal indicates a condition corresponding to the second threshold value requiring actuation of said safety restraint; and wherein said second switch means is in communication with said processor means (24) and, in use, closes in response to generation of said second signal; said failure detecting means (44) is additionally for detecting a failure of said sensor means (26) and/or said processor means (24); said shunt means (46) is additionally for shunting said second switch means (22) upon detection of a failure of said sensor means (26) and/or said processor means (24); and said threshold adjusting means (36,38) also operates to increase the threshold value of said first switch means (14,16) upon

detection of a failure of said sensor means (26) and/or processor means (24) and wherein operation of said threshold-adjusting means (36,38) is, in use, inhibited upon detection of a failure of said first switch means (14,16).

#### US 5261694A

The control circuit for a vehicle passenger restraint includes a firing path including in series: a first, normally-open, acceleration-responsive switch which closes in response to an acceleration input exceeding a first threshold, the first switch being shunted by a first shunting resistor. A trigger actuates the restraint. The trigger having internal electrical resistance less than the resistance of the first shunting resistor. Second and third normally-open, electrically-operated switches are provided. The second switch is shunted by a second shunting resistor having a resistance greater than the internal resistance of the trigger. A device applies a voltage across the firing path. An electronic sensor detects an acceleration exceeding a second threshold, which is nominally greater than the first threshold.

A microprocessor responds to the electronic sensor for operating the controlling the second switch. The microprocessor closes the second switch when the electronic sensor senses an acceleration exceeding the second threshold. A failure-detector senses a failure of first switch, the electronic sensor, the microprocessor, or the second switch. A first device responds to the failure-detector for increasingly biasing the first switch in the normally-open position. A second device responds to the failure-detector by operating the third switch.

USE/ADVANTAGE - for vehicle passenger restraint e.g. air bags. Continuing circuit viability notwithstanding single point failure.

CHOSEN-DRAWING: Dwg.1/1 Dwg.1/1 Dwg.1/1

DERWENT-CLASS: Q17 S02 T01 X22 EPI-CODES: S02-G03; T01-J07C; X22-J07;

## Previous Doc Next Doc Go to Doc#

First Hit Your wildcard search against 10000 terms has yielded the results below. Your result set for the last L# is incomplete.

The probable cause is use of unlimited truncation. Revise your search strategy to use limited truncation.

| Clear | Generate Collection | Print    | Ewd Refs | Bkwd Refs |

|-------|---------------------|----------|----------|-----------|

|       | Gener               | ate OACS |          |           |

Search Results - Record(s) 1 through 7 of 7 returned.

Document ID: US 5668723 A 1. Using default format because multiple data bases are involved. L16: Entry 1 of 7 File: USPT Sep 16, 1997 US-PAT-NO: 5668723 DOCUMENT-IDENTIFIER: US 5668723 A TITLE: Method and apparatus for sensing a vehicle crash using crash energy DATE-ISSUED: September 16, 1997 INVENTOR-INFORMATION: NAME CITY STATE ZIP CODE COUNTRY Blackburn; Brian K. Rochester MI US-CL-CURRENT: 701/45 1300 (-

| Full Title Citation Front Review                                                           | Classification Date Reference               | Claims (1990) fr       |

|--------------------------------------------------------------------------------------------|---------------------------------------------|------------------------|

| □ 2. Document ID:                                                                          | US 5216607 A                                |                        |

| L16: Entry 2 of 7                                                                          | File: USPT                                  | Jun 1, 1993            |

| US-PAT-NO: 5216607<br>DOCUMENT-IDENTIFIER: US 52166<br>** See image for <u>Certificate</u> |                                             |                        |

| TITLE: Method and apparatus is measures of crash violence                                  | For sensing a <u>vehicle</u> crash usi<br>e | ng energy and velocity |

Title Citation Front Review Classification Date Reference 10000 Craw C Full

## □ 3. Document ID: US 4990884 A

L16: Entry 3 of 7

US-PAT-NO: 4990884 DOCUMENT-IDENTIFIER: US 4990884 A

TITLE: Method and apparatus for testing an airbag restraint system

Full Title Citation Front Review Classification Date Reference

File: USPT

□ 4. Document ID: US 4835513 A

L16: Entry 4 of 7

File: USPT

May 30, 1989

US-PAT-NO: 4835513 DOCUMENT-IDENTIFIER: US 4835513 A \*\* See image for <u>Certificate of Correction</u> \*\*

TITLE: Method and apparatus for testing an airbag restraint system

Full Title Citation Front Review Classification Date Reference Reference Contraction Clasmic Contraction Craw C

□ 5. Document ID: US 5872460 A

L16: Entry 5 of 7

File: DWPI

Feb 16, 1999

DERWENT-ACC-NO: 1999-166796 DERWENT-WEEK: 199914 COPYRIGHT 2006 DERWENT INFORMATION LTD

TITLE: <u>FET</u> based firing circuit test apparatus in supplemental inflatable <u>restraint</u> (SIR) system

Full Title Citation Front Review Classification Date Reference Control Control Claims 10000 Draw D

□ 6. Document ID: US 5666065 A

L16: Entry 6 of 7

File: DWPI

Sep 9, 1997

DERWENT-ACC-NO: 1997-456916 DERWENT-WEEK: 199742 COPYRIGHT 2006 DERWENT INFORMATION LTD

TITLE: Test circuit for <u>FETs</u> of firing circuit of inflatable <u>restraint</u> system of <u>vehicle</u> - biasses squib to intermediate voltage and turns on each <u>FET</u> alone to apply battery or ground voltage to squib, and high and low voltage detectors sense voltage excursion past respective thresholds to verify FET operation

#### Feb 5, 1991

Full Title Citation Front Review Classification Date Reference Company Claims MMC Draw

## □ 7. Document ID: EP 518501 A1, KR 126667 B1, AU 9218036 A, CA 2069214 A, US 5261694 A, EP 518501 B1, DE 69209151 E, CA 2069214 C

L16: Entry 7 of 7 Fil

File: DWPI

Dec 16, 1992

DERWENT-ACC-NO: 1992-417372 DERWENT-WEEK: 199952 COPYRIGHT 2006 DERWENT INFORMATION LTD

TITLE: <u>Vehicle</u> passenger <u>restraint</u> firing circuit – uses microprocessor to control operation with diagnostic ASIC monitoring crash sensor to bias safer sensor and replace inoperable <u>FET</u> under failure conditions

Full Title Citation Front Review Classification Date Reference The Chairman Clairman 1300C Draw D

Clear Generate Collection Print Ewd Refs Bkwd Refs Generate OACS

| Terms         | Documents |

|---------------|-----------|

| L15 and FET\$ | 7         |

Display Format: - Change Format

Previous Page Next Page Go to Doc#

|              |                        | Fwd Refs                                                         | Previous                  | Doc          | <u>Next Do</u> | <u>c Go</u> | to Doc#      |

|--------------|------------------------|------------------------------------------------------------------|---------------------------|--------------|----------------|-------------|--------------|

| En           | d of Re                | sult Set                                                         |                           |              |                |             |              |

|              |                        |                                                                  | Generate:                 | Collection   | Print          |             |              |

|              | ~                      |                                                                  |                           |              |                |             |              |

| L            | 18: Entry              | 7 1 of 1                                                         |                           | File: (      | JSPT           |             | Nov 16, 1993 |

| DOCU         |                        | <u>261694</u><br>NTIFIER: US 526<br><b>for <u>Certificat</u></b> |                           | <u>on</u> ** |                |             |              |

| TITI         | E: Recon               | figurable air b                                                  | ag firing circ            | uit          |                |             |              |

| DATE         | -ISSUED:               | November 16, 1                                                   | 993                       |              |                |             |              |

|              |                        | ORMATION:                                                        |                           |              |                |             |              |

| NAMI         | _                      |                                                                  | ITY                       |              |                | CODE        | COUNTRY      |

|              | te; Craig<br>ser; Kevi |                                                                  | rosse Pointe<br>armington | MI<br>MI     |                |             |              |

|              | e; James               |                                                                  | oseville                  | MI           |                |             |              |

| -            |                        |                                                                  |                           |              |                |             |              |

|              |                        | ORMATION:                                                        |                           |              |                |             |              |

| NAMI         |                        |                                                                  | CITY                      |              | STATE ZIP C    | ODE COUNTE  | RY TYPE CODE |

| Auto<br>Inc. |                        | ystems Laborato                                                  | ry, Farmingt<br>Hills     | on           | MI             |             | 02           |

|              | -NO: 07/<br>FILED:     | 715344 <u>[PALM]</u><br>June 14, 1991                            |                           |              |                |             |              |

| INT-         | CL-ISSUE               | D: [05] B60R 21,                                                 | /16                       |              |                |             |              |

|              |                        | : 280/735; 307/<br>I: <u>280/735</u> ; <u>307</u> ,              |                           |              |                |             |              |

| FIEL<br>340/ |                        | SSIFICATION-SEA                                                  | RCH: 280/735,             | 180/274,     | 180/282, 3     | 307/10.1,   | 340/436,     |

| See          | applicat               | ion file for con                                                 | mplete search             | history.     |                |             |              |

| PRIO         | R-ART-DI               | SCLOSED:                                                         |                           |              |                |             |              |

|              |                        |                                                                  | U.S. PATEN                | IT DOCUM     | ENTS           |             |              |

|              |                        | Sea                                                              | rch Selected              | Search /     | NLL Clea       | I           |              |

|              | PAT-NO                 | ISSUE-DAT                                                        | E                         | PATEN        | ree-name       | US          | -CL          |

|              | 4851705                | July 1989                                                        |                           |              | r et al.       |             | 0/735        |

|              | 4958851                | _                                                                |                           | Behr         | et al.         |             | 0/735        |

| _            |                        | -                                                                |                           |              |                |             |              |

.

•

White

73/1D

5060504 October 1991

5085464

340/436

ART-UNIT: 316

PRIMARY-EXAMINER: Tyson; Karin L. ATTY-AGENT-FIRM: Lyon & Delevie

ABSTRACT:

An air bag firing circuit comprises a firing path which includes in series a safing sensor, a squib, and a FET operated under microprocessor control in response to the output of an electronic crash sensor. A power supply maintains a known voltage across the firing path sufficient to explode the squib upon simultaneous "closure" of both the safing sensor and the FET operated by the microprocessor in response to crash sensor output. Normally, upon detection of a failure in the electronic crash sensor, its supporting electronics, or the FET actuated in response thereto, the microprocessor reconfigures the firing threshold of the safing sensor, as by applying a current to its integral test coil to increasingly bias the sensor's inertial mass away from its switch contacts. However, if a failure of the safing sensor is detected, reconfiguration of its threshold is inhibited notwithstanding the failure of other circuit components to prevent inadvertent deployment of the air bag. Once the safing sensor is reconfigured, the microprocessor turns on another FET to pull one side of the squib to ground, thereby removing the inoperable FET from the firing path and ensuring continued protection of the vehicle passengers until the sensor is serviced or replaced.

5 Claims, 1 Drawing figures

Previous Doc Next Doc

Go to Doc#

## <u>First Hit</u> <u>Fwd Refs</u> End of Result Set

Previous Doc N

Next Doc Go to Doc#

Generate Collection Print

L20: Entry 1 of 1

File: USPT

Nov 16, 1993

DOCUMENT-IDENTIFIER: US 5261694 A \*\* See image for <u>Certificate of Correction</u> \*\* TITLE: Reconfigurable air bag firing circuit

#### Abstract Text (1):

An air bag firing circuit comprises a firing path which includes in series a safing sensor, a squib, and a FET operated under microprocessor control in response to the output of an electronic crash sensor. A power supply maintains a known voltage across the firing path sufficient to explode the squib upon simultaneous "closure" of both the safing sensor and the FET operated by the microprocessor in response to crash sensor output. Normally, upon detection of a failure in the electronic crash sensor, its supporting electronics, or the FET actuated in response thereto, the microprocessor reconfigures the firing threshold of the safing sensor, as by applying a current to its integral test coil to increasingly bias the sensor's inertial mass away from its switch contacts. However, if a failure of the safing sensor is detected, reconfiguration of its threshold is inhibited notwithstanding the failure of other circuit components to prevent inadvertent deployment of the air bag. Once the safing sensor is reconfigured, the microprocessor turns on another <u>FET</u> to pull one side of the squib to ground, thereby removing the inoperable FET from the firing path and ensuring continued protection of the vehicle passengers until the sensor is serviced or replaced.

#### Brief Summary Text (10):

The improved control circuit for a vehicle passenger safety restraint of the instant invention comprises a low-threshold acceleration sensor, or "safing sensor," whose acceleration-responsive switch is connected in series with an explosive squib and a <u>FET</u>, with the FET closing under microprocessor control in response to the output of an electronic sensor employing a relatively-higher threshold. Upon the detection of a failure of the crash-discriminating electronic acceleration sensor functionality, the circuit reconfigures the firing circuit by raising the acceleration threshold of the safing sensor and then, after a suitable delay, removing the <u>FET</u> from the firing path by pulling down the side of the squib opposite the safing sensor to ground. In the preferred embodiment of the invention, the safing sensor is tested, and its threshold alternatively raised, by passing a current from a constant current source through a test coil integral to the sensor, as controlled by an application specific integrated circuit.

#### Detailed Description Text (2):

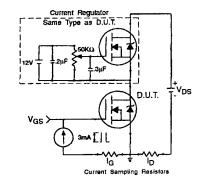

Referring to the drawing, an exemplary air bag firing circuit 10 according to the instant invention comprises a firing path 12 which includes, in series, the normally-open, relatively-low-threshold acceleration-responsive switch 14 of an acceleration sensor (hereinafter "safing sensor 16"); and parallel firing path legs 18a and 18b each having in series an explosive squib 20 for triggering deployment of a driver's-side and a passenger's-side air bag, respectively (both not shown), and a <u>FET</u> ("firing <u>FET</u> 22") for pulling down the side of each squib 20 opposite the safing sensor 16 to ground when operated by a microprocessor 24. The microprocessor

24 is itself responsive to the output of an electronic crash sensor integrated within an Application Specific Integrated Circuit ("Sensor ASIC 26"), as more fully described below.

#### Detailed Description Text (3):

A power supply 28 applies a known supply voltage V.sub.s across the firing path 12 sufficient to explode each squib 20 upon the simultaneous closure of the safing sensor's switch 14 and the firing  $\underline{FET}$  22 connected to the squib 20. The power supply 28 includes a capacitor 30 and charge pump 32 to maintain the applied voltage V.sub.s if the battery 34 connected thereto malfunctions or is otherwise isolated therefrom during a vehicle collision.

#### Detailed Description Text (5):

Similarly, a constructed embodiment of the crash sensor integrated into the Sensor ASIC 26 is disclosed in our co-pending U.S. patent application Ser. No. 07/413,318 filed Sep. 27, 1989, now U.S. Pat. No. 5,060,504 issued Oct. 29, 1991, and entitled "Self-Calibrating Accelerometer," which teaching is also hereby incorporated herein by reference. Simply stated, the electronic sensor within the Sensor ASIC 26 provides an analog output proportional to vehicle acceleration, as through the incorporation of a piezoresistive element in the support beam of the sensor's micromachined cantilevered inertial mass. After analog-to-digital conversion of the electronic sensor's output within the Sensor ASIC 26, the resulting acceleration data is communicated to the microprocessor 24 via a Serial Peripheral Interface ("SPI 40"), whereupon the microprocessor 24 determines whether a threshold acceleration has been exceeded, thereby indicating a crash condition. If a crash condition is indicated, the microprocessor 24 turns on the firing <u>FETs</u> 22 to pull down the side of each squib 20 opposite the safing sensor 16 to ground.

#### Detailed Description Text (6):

The normally-open switch 14 of the safing sensor 16 and each firing <u>FET</u> 22 are shunted by a resistor 42 of like nominal resistance. Preferably, the nominal resistance of the shunting resistors 42 is several orders of magnitude larger than the nominal internal resistance of each of the squibs 20. In normal operation, the shunting resistors 42 maintain a relatively-low current flow through the firing path 12 and, hence, through the squibs 20 thereof. Upon the simultaneous closure of the safing sensor 16 and the firing <u>FETS</u> 22 in response to an acceleration exceeding the respective thresholds of the safing sensor 16 and the electronic crash sensor within the ASIC 26 (as determined by the microprocessor 24), the shunting resistors 42 are shorted and the current flowing through each squib 20 increases to a value above the firing threshold thereof to explode same and trigger deployment of each air bag.

#### Detailed Description Text (8):

An additional <u>FET</u> ("reconfiguration <u>FET</u> 46") is connected to the firing path 12 at points on each leg 18a and 18b between the squib 20 and the firing <u>FET</u> 22 thereon via a diode 48, with the reconfiguration <u>FET</u> 46 being controlled by the Sensor ASIC 26. The reconfiguration <u>FET</u> 46 allows the Sensor ASIC 26 to pull the side of each squib 20 opposite the safing sensor 16 to ground when the Diagnostic ASIC 44 detects a failure of the Sensor ASIC's integral electronic crash sensor or its supporting electronics, including failures of the microprocessor 24 or the <u>FETs</u> 22 controlled by the microprocessor 24.

#### Detailed Description Text (9):

Under the instant invention, reconfiguration of the circuit's firing path 12 is controlled by the two ASICs 26 and 44, the constant current source 36, and the microprocessor 24, as follows: in the circuit's normal mode of operation, the microprocessor 24 initiates firing-path reconfiguration through the use of a watchdog timer in the Diagnostic ASIC 44. Specifically, the microprocessor 24 periodically resets the timer by sending reconfiguration pulses 50 to the Diagnostic ASIC 44. If the microprocessor 24 detects a failure of the Sensor ASIC 26, e.g., the failure of its electronic crash sensor to properly respond to acceleration, or excessive electromagnetic interference ("EMI"), the microprocessor 24 stops transmitting reconfiguration pulses 50 to the Diagnostic ASIC 44, and the timer runs out to trigger reconfiguration. Similarly, the microprocessor 24 will request reconfiguration of the circuit's firing path 12 upon detecting a failure of any of the firing <u>FETs</u> 22 or the reconfiguration <u>FET</u> 46. A suitable period for the watchdog timer is believed to be about 250 msec.

#### Detailed Description Text (12):

Once triggered, the reconfiguration sequence for the instant circuit 10 is as follows: the Diagnostic ASIC 44 first determines whether the safing sensor 16 has been shorted to ground by monitoring the voltage at a point 58 on the firing path 12 between the safing sensor 16 and both squibs 20. If continuing safing sensor functionality (and firing path integrity) is confirmed, the Diagnostic ASIC 44 will send signals 62, 64, and 66 through PHASE, I.sub.0 and I.sub.1 terminals of the constant current source 36, respectively, whereby the current 60 is directed in a second direction through the sensor's test coil 38 to increase its threshold by increasingly biasing its switch 14 in the open position. When the current source 36 is turned on, the current source 36 also generates current sense pulses 68 which are counted by the Sensor ASIC 26. After a suitable number of pulses 68 are counted by the Sensor ASIC 26, thereby representing a reasonable time delay to permit the reconfigured safing sensor 16 to achieve a steady-state heightened threshold, the Sensor ASIC 26 turns on the reconfiguration FET 46 to pull down the sides of the squibs 20 opposite the safing sensor 16 to ground. The firing path 12 of the instant circuit 10 is thus reconfigured, with the heightened-threshold safing sensor 16 thereafter operating as the circuit's crash-discriminating sensor.

#### Detailed Description Text (14):

If the monitored voltage at point 58 on the firing path 12 indicates a shorted safing sensor 16, the Diagnostic ASIC 44 terminates the reconfiguration sequence, since it otherwise might result in inadvertent deployment of the air bags if the reconfiguration <u>FET</u> 46 would thereafter be turned on.

#### Detailed Description Text (16):

While the preferred embodiment of the invention has been disclosed, it should be appreciated that the invention is susceptible of modification without departing from the spirit of the invention or the scope of the subjoined claims. For example, under the instant invention, the Sensor and Diagnostic ASICs 26 and 44 may be repackaged so as to place all reconfiguration control in a separate Reconfiguration ASIC which is therefore wholly independent from the components providing diagnostic capability. Such a reconfiguration ASIC would preferably incorporate V.sub.s, current sense, and voltage monitoring inputs; PHASE, I.sub.0, I.sub.1, reconfiguration <u>FET</u> control, and reconfiguration pulse outputs; and SPI communication with other circuit components regarding electronic sensor output, test signal requests, and other circuit component status communication.

## Previous Doc Next Doc Go to Doc#

Hit List

First Hit Your wildcard search against 10000 terms has yielded the results below. Your result set for the last L# is incomplete.

The probable cause is use of unlimited truncation. Revise your search strategy to use limited truncation.

Clear

Generate Collection

Print

Fwd Refs

Bkwd Refs

Generate OACS

Search Results - Record(s) 1 through 7 of 7 returned.

Document ID: US 5668723 A  $\square$  1. Using default format because multiple data bases are involved. L16: Entry 1 of 7 File: USPT Sep 16, 1997 US-PAT-NO: 5668723 DOCUMENT-IDENTIFIER: US 5668723 A TITLE: Method and apparatus for sensing a vehicle crash using crash energy DATE-ISSUED: September 16, 1997 INVENTOR-INFORMATION: NAME CITY STATE ZIP CODE COUNTRY Blackburn; Brian K. Rochester MI US-CL-CURRENT: 701/45 Title Citation Front Review Classification Date Reference Claims Claims 10000 Draws ( □ 2. Document ID: US 5216607 A L16: Entry 2 of 7 File: USPT Jun 1, 1993

US-PAT-NO: 5216607 DOCUMENT-IDENTIFIER: US 5216607 A \*\* See image for <u>Certificate of Correction</u> \*\*

TITLE: Method and apparatus for sensing a  $\underline{vehicle}$  crash using energy and velocity as measures of crash violence

Full Title Citation Front Review Classification Date Reference Contained Claims 10040 Grave D

## □ 3. Document ID: US 4990884 A

L16: Entry 3 of 7 Fi

US-PAT-NO: 4990884 DOCUMENT-IDENTIFIER: US 4990884 A

TITLE: Method and apparatus for testing an airbag restraint system

Full Title Citation Front Review Classification Date Reference France Classification Claims Field Draw C

□ 4. Document ID: US 4835513 A

L16: Entry 4 of 7

File: USPT

May 30, 1989

US-PAT-NO: 4835513 DOCUMENT-IDENTIFIER: US 4835513 A \*\* See image for <u>Certificate of Correction</u> \*\*

TITLE: Method and apparatus for testing an airbag restraint system

Full Title Citation Front Review Classification Date Reference

□ 5. Document ID: US 5872460 A

L16: Entry 5 of 7

File: DWPI

Feb 16, 1999

DERWENT-ACC-NO: 1999-166796 DERWENT-WEEK: 199914 COPYRIGHT 2006 DERWENT INFORMATION LTD

TITLE: <u>FET</u> based firing circuit test apparatus in supplemental inflatable <u>restraint</u> (SIR) system

□ 6. Document ID: US 5666065 A

L16: Entry 6 of 7

File: DWPI

Sep 9, 1997

DERWENT-ACC-NO: 1997-456916 DERWENT-WEEK: 199742 COPYRIGHT 2006 DERWENT INFORMATION LTD

TITLE: Test circuit for <u>FETs</u> of firing circuit of inflatable <u>restraint</u> system of <u>vehicle</u> - biasses squib to intermediate voltage and turns on each <u>FET</u> alone to apply battery or ground voltage to squib, and high and low voltage detectors sense voltage excursion past respective thresholds to verify FET operation

Feb 5, 1991

$\sim$

File: USPT

Full Title Citation Front Review Classification Date Reference

# □ 7. Document ID: EP 518501 A1, KR 126667 B1, AU 9218036 A, CA 2069214 A, US 5261694 A, EP 518501 B1, DE 69209151 E, CA 2069214 C

L16: Entry 7 of 7 File: DWPI

Dec 16, 1992

J

DERWENT-ACC-NO: 1992-417372 DERWENT-WEEK: 199952 COPYRIGHT 2006 DERWENT INFORMATION LTD

1 2

TITLE: <u>Vehicle</u> passenger <u>restraint</u> firing circuit - uses microprocessor to control operation with diagnostic ASIC monitoring crash sensor to bias safer sensor and replace inoperable <u>FET</u> under failure conditions

Print

Full Title Offation Front Review Classification Date Reference Frence Claims Claims Dool Draws for

Clear Generate Collection

Fwd Refs Bkwd Refs

Generate OACS

| Terms         | Documents |

|---------------|-----------|

| L15 and FET\$ | 7         |

Display Format: - Change Format

Previous Page Next Page Go to Doc#

| <u>First Hit</u> Fwo                 | 00000000                  | Cevious Doc<br>Generate Collec |                       | oc <u>Go</u> | to Doc#      |

|--------------------------------------|---------------------------|--------------------------------|-----------------------|--------------|--------------|

|                                      | . · · · ·                 |                                |                       |              |              |

| L16: Entry 1 o                       | of 7                      | Fil                            | e: USPT               |              | Sep 16, 1997 |

| US-PAT-NO: 56687<br>DOCUMENT-IDENTIF | 723<br>FIER: US 5668723 A |                                |                       |              |              |

| TITLE: Method an                     | nd apparatus for so       | ensing a <u>veh</u>            | <u>nicle</u> crash us | ing crash    | energy       |

| DATE-ISSUED: Sep                     | tember 16, 1997           |                                |                       |              |              |

| INVENTOR-INFORMA                     | TION:                     |                                |                       |              |              |

| NAME                                 | CI                        | ТҮ                             | STATE ZIP             | CODE         | COUNTRY      |

| Blackburn; Brian                     | ıK. Ro                    | chester                        | MI                    |              |              |

| ASSIGNEE-INFORMA                     | TION:                     |                                |                       |              |              |

| NAME                                 |                           | CITY                           | STATE ZIP COL         | E COUNTRY    | TYPE CODE    |

| TRW <u>Vehicle</u> Safe              | ety Systems Inc.          | Lyndhurst                      | ОН                    |              | 02           |

| APPL-NO: 08/6504                     | 24 [PALM]                 |                                |                       |              |              |

APPL-NO: 08/650424 [PALM] DATE FILED: May 20, 1996

#### PARENT-CASE:

RELATED APPLICATIONS This application is a continuation-in-part of U.S. patent application Ser. No. 07/818,280, filed Jan. 8, 1992, now U.S. Pat. No. 5,546,307 entitled "METHOD AND APPARATUS FOR DISCRIMINATING <u>VEHICLE</u> CRASH CONDITIONS" filed in the name of Joseph F. Mazur et al. which is a continuation-in-part of U.S. Ser. No. 07/520,417, filed May 11, 1990, in the name of Diller et al., entitled METHOD AND APPARATUS FOR SENSING A <u>VEHICLE</u> CRASH USING ENERGY AND VELOCITY AS MEASURES OF CRASH VIOLENCE" which is now U.S. Pat. No. 5,216,607, issued Jun. 1, 1993, which is a continuation-in-part of U.S. Ser. No. 07/358,875, filed May 30, 1989, in the name of Brian K. Blackburn entitled "METHOD AND APPARATUS FOR SENSING A <u>VEHICLE</u> CRASH", which is now U.S. Pat. No. 4,979,763 issued Dec. 25, 1990.

INT-CL-ISSUED: [06] <u>B60</u> <u>R</u> <u>21/32</u>

US-CL-ISSUED: 701/45 US-CL-CURRENT: 701/45

FIELD-OF-CLASSIFICATION-SEARCH: 364/424.055, 364/424.056, 364/424.057, 180/282, 180/232, 180/271, 280/728, 280/734, 280/735, 340/438, 340/436, 307/9.1, 307/10.1 See application file for complete search history.

PRIOR-ART-DISCLOSED:

#### U.S. PATENT DOCUMENTS

Search Selected Search ALL Clear

| PAT-NO         | ISSUE-DATE     | PATENTEE-NAME  | US-CL     |

|----------------|----------------|----------------|-----------|

| 3703300        | November 1972  | Gillund et al. | 280/150AB |

| 3870894        | March 1975     | Brede et al.   | 307/9     |

| <u>3911391</u> | October 1975   | Held et al.    | 340/52H   |

| 4020453        | April 1977     | Spies et al.   | 340/52H   |

| 4166641        | September 1979 | Okada et al.   | 280/735   |

| 4638179        | January 1987   | Mattes et al.  | 307/105B  |

| 4804859        | February 1989  | Swart          | 307/105B  |

| 4842301        | June 1989      | Feldmaier      | 280/735   |

| <u>4851705</u> | July 1989      | Musser et al.  | 307/10.1  |

| 4873452        | October 1989   | Morota et al.  | 307/10.1  |

ART-UNIT: 234

PRIMARY-EXAMINER: Teska; Kevin J.

ASSISTANT-EXAMINER: Walder, Jr.; Stephen J.

ATTY-AGENT-FIRM: Tarolli, Sundheim, Covell, Tummino & Szabo

ABSTRACT:

A method and apparatus is disclosed for providing a passenger restraint actuation signal for use in an actuatable passenger restraint system in a vehicle is provided. A sensor provides a signal indicative of crash acceleration. A crash energy value is determined from the crash acceleration signal and is compared against an energy threshold value. If the determined crash energy value equals or exceeds the energy threshold value, a passenger restraint actuation signal is provided.

2 Claims, 13 Drawing figures

Previous Doc Next Doc Go to Doc#

### <u>First Hit</u>

## Previous Doc Next Doc Go to Doc#

Generate Collection Print

L16: Entry 5 of 7

File: DWPI

Search ALL

Clear

Feb 16, 1999

DERWENT-ACC-NO: 1999-166796 DERWENT-WEEK: 199914 COPYRIGHT 2006 DERWENT INFORMATION LTD

TITLE: <u>FET</u> based firing circuit test apparatus in supplemental inflatable <u>restraint</u> (SIR) system

INVENTOR: ANDERSON, T; BENNETT, P T ; CONSTABLE, R K ; GRAY, R C ; RAVAS, R J

PATENT-ASSIGNEE: DELCO ELECTRONICS CORP (DELCN)

PRIORITY-DATA: 1996US-0726897 (October 4, 1996)

Search Selected

PATENT-FAMILY:

| PUB-NO              | PUB-DATE          | LANGUAGE | PAGES | MAIN-IPC   |

|---------------------|-------------------|----------|-------|------------|

| <u>US 5872460 A</u> | February 16, 1999 |          | 011   | G01R031/26 |

APPLICATION-DATA:

| PUB-NO      | APPL-DATE       | APPL-NO        | DESCRIPTOR |

|-------------|-----------------|----------------|------------|

| US 5872460A | October 4, 1996 | 1996US-0726897 |            |

INT-CL (IPC): <u>B60 R 21/32; G01 R 31/26</u>

ABSTRACTED-PUB-NO: US 5872460A BASIC-ABSTRACT:

NOVELTY - The gate drive circuits (26,28) are connected with logic module (42) that responds to detection results of current detectors (32,50) and voltage detectors (38,40). When the short condition is indicated by the detection result of the current detector, the selected <u>FET</u> is turned OFF, independent of the microprocessor based deployment controller (12).

DETAILED DESCRIPTION - The gate drive circuits (26,28) turn on a selected <u>FET</u> to test operability of such <u>FET</u>, in response from a microprocessor based deployment controller. The current detector detects firing circuit current and if this detection results exceeds current threshold, short condition is indicated. The voltage detectors are also connected to the firing circuit for detecting whether variance of voltage on squib between <u>FETs</u> serially coupled between voltage source and ground, exceeds set voltage threshold values where the threshold values are above and below a regulated voltage applied to the squib. When the detection result of the voltage detector indicates that detected voltage on squib breaches one of the voltage threshold values, then the selected FET is disabled.

USE - For supplemental inflatable restraint system for inflating airbag in

#### automotive vehicles.

ADVANTAGE - Facilitates rapid testing of <u>FETs</u> of SIR firing circuit even when it is subjected to wide ranges of voltages due to shorts. Even in case of resistive short, the short is detected by sensing abnormal loop voltage and thus turns off the selected <u>FET</u>. <u>FETs</u> of the SIR firing loop is tested without any danger of firing the squib even when short condition occurs.

DESCRIPTION OF DRAWING(S) - The figure depicts the SIR control for inflating airbag of automotive <u>vehicle</u>.

Microprocessor based deployment controller 12

Gate drive circuits 26,28

Current detectors 32,50

Voltage detectors 38,40

Logic module 42

ABSTRACTED-PUB-NO: US 5872460A EQUIVALENT-ABSTRACTS:

CHOSEN-DRAWING: Dwg.1/5

DERWENT-CLASS: Q17 S01 S02 U11 EPI-CODES: S01-G02B; S02-J02E; U11-F01C5;

Previous Doc Next Doc (

Go to Doc#

| <u>First Hit</u> <u>Fwd Refs</u><br>End of Result Set                            | Previou                 | <u>s Doc</u>     | <u>Next Doc</u>      | Go to Doc#             |

|----------------------------------------------------------------------------------|-------------------------|------------------|----------------------|------------------------|

|                                                                                  | Generat                 | e Collection     | Print                |                        |

| L14: Entry 1 of 1                                                                |                         | File:            | USPT                 | Jul 4, 1995            |

| US-PAT-NO: <u>5430314</u><br>DOCUMENT-IDENTIFIER: US                             | 5430314 A               |                  |                      |                        |

| TITLE: Power device with                                                         | buffered gate a         | shield re        | gion                 |                        |

| DATE-ISSUED: July 4, 199                                                         | 95                      |                  |                      |                        |

| INVENTOR-INFORMATION:<br>NAME                                                    | CITY                    | CMAME            |                      | COUNTRY                |

| NAME<br>Yilmaz; Hamza                                                            | Saratoga                | STATE<br>CA      | ZIP CODE             | COUNTRY                |

| ASSIGNEE-INFORMATION:                                                            |                         |                  |                      |                        |

| NAME<br>Siliconix Incorporated                                                   | CITY<br>Santa Clara     |                  | ZIP CODE CO          | OUNTRY TYPE CODE<br>02 |

| APPL-NO: 07/873423 [PF<br>DATE FILED: April 23, 19                               |                         |                  |                      |                        |

| INT-CL-ISSUED: [06] <u>H01</u>                                                   | <u>L 29/10, H01 L 2</u> | <u>29/78, но</u> | <u>1 L 27/14, но</u> | <u>01 L 31/00</u>      |

| US-CL-ISSUED: 257/328; 2<br>US-CL-CURRENT: <u>257/328;</u><br><u>257/E29.257</u> |                         |                  |                      | <u>257/E29.066</u> ,   |

| FIELD-OF-CLASSIFICATION-<br>257/341<br>See application file for                  |                         |                  |                      | 57/337, 257/340,       |

| PRIOR-ART-DISCLOSED:                                                             |                         | -<br>-           |                      |                        |

|                                                                                  | U.S. PAT                | ENT DOCUM        | ENTS                 |                        |

|                                                                                  | Search Selected         | Search           | ALL                  |                        |

| PAT-NO ISSUE-                                                                    | DATE                    | PATENTE          | E-NAME               | US-CL                  |

| ☐ 4532534 July 1                                                                 | 985                     | Ford et          | al.                  | 357/23.4               |

.

•

.

| 4532534        | July 1985                                          | Ford et al.                                                                                               | 357/23.4                                                                                                                                                                |

|----------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4631564        | December 1986                                      | Neilson et al.                                                                                            | 357/23.4                                                                                                                                                                |

| 4819044        | April 1989                                         | Murakami                                                                                                  |                                                                                                                                                                         |

| 4985739        | January 1991                                       | Lapham et al.                                                                                             | 357/22                                                                                                                                                                  |

| <u>5136349</u> | August 1992                                        | Yilmaz et al.                                                                                             | 357/23.4                                                                                                                                                                |

|                | <u>4631564</u><br><u>4819044</u><br><u>4985739</u> | 4631564         December 1986           4819044         April 1989           4985739         January 1991 | 4631564         December 1986         Neilson et al.           4819044         April 1989         Murakami           4985739         January 1991         Lapham et al. |

#### FOREIGN PATENT DOCUMENTS

| FOREIGN-PAT-NO | PUBN-DATE     | COUNTRY | CLASS |

|----------------|---------------|---------|-------|

| 293846A1       | May 1988      | EP      |       |

| 335750A3       | April 1989    | EP      |       |

| 60-249367      | December 1985 | JP      |       |

| 61-80860       | April 1986    | JP      |       |

| 61-84865       | April 1986    | JP      |       |

| 63-73564       | April 1988    | JP      |       |

| 63-84070       | April 1988    | JP      |       |

| 1-276770       | November 1989 | JP      |       |

| 2-35780        | February 1990 | JP      |       |

| 3173180        | July 1991     | JP      |       |

| 2137811        | October 1984  | GB      |       |

| 2166290        | April 1986    | GB      |       |

|                |               |         |       |

#### OTHER PUBLICATIONS

Conference Record of the 1986 IEEE Industry Applications Society Annual Meeting, vol. 1, Oct. 1986, Denver, Colo., "Optimization of Power MOSFET Body Diode for Speed and Ruggedness", by Hamza Yilmaz et al., pp. 330-334. "Design Optimization of Power MOSFET With Built-In Flyback Diode", by Yilmaz et al., Power Electronics Semiconductor Department, General Electric Co., Syracuse, N.Y., pp. 1-6. "MOSPOWER Applications Handbook", Severns et al., Siliconix Incorporated, 1984, pp. 5-57 through 5-64. "Semiconductor Power Devices", Sorab K. Ghandhi, Rensselaer Polytechnic Institute, John Wiley & Sons, N.Y., 1977, pp. 1-17 and 172-176.

ART-UNIT: 253

PRIMARY-EXAMINER: Crane; Sara W.

ASSISTANT-EXAMINER: Wallace; Valencia M.

ATTY-AGENT-FIRM: Skjerven, Morrill, MacPherson, Franklin & Friel

ABSTRACT:

The present invention provides a gate buffer region between a gate shield region and active cells of a power device. This gate buffer region may, for example, be a relatively narrow, strip-like doped region which extends into an epitaxial layer from an upper surface of the epitaxial layer. The gate shield region is connected to a source electrode of the power device via a relatively high impedance connection. The gate buffer region, on the other hand, is connected to the source electrode with a relatively low impedance connection. This relatively low impedance connection may, for example, be a substantially direct metallized connection from a metal source electrode to the gate buffer region at the surface of the epitaxial layer.

15 Claims, 18 Drawing figures

First Hit

## Previous Doc Next Doc Go to Doc#

Generate Collection Print

L16: Entry 6 of 7

File: DWPI

Sep 9, 1997

DERWENT-ACC-NO: 1997-456916 DERWENT-WEEK: 199742 COPYRIGHT 2006 DERWENT INFORMATION LTD

TITLE: Test circuit for <u>FETs</u> of firing circuit of inflatable <u>restraint</u> system of <u>vehicle</u> - biasses squib to intermediate voltage and turns on each <u>FET</u> alone to apply battery or ground voltage to squib, and high and low voltage detectors sense voltage excursion past respective thresholds to verify FET operation

INVENTOR: ANDERSON, T; CONSTABLE, R K ; RAVAS, R J

PATENT-ASSIGNEE: DELCO ELECTRONICS CORP (DELCN)

PRIORITY-DATA: 1996US-0651073 (May 22, 1996)

Search Selected Search ALL Clear

PATENT-FAMILY:

| PUB-NO              | PUB-DATE          | LANGUAGE | PAGES | MAIN-IPC   |

|---------------------|-------------------|----------|-------|------------|

| <u>US 5666065 A</u> | September 9, 1997 |          | 007   | G01R031/28 |

APPLICATION-DATA:

| PUB-NO      | APPL-DATE    | APPL-NO        | DESCRIPTOR |

|-------------|--------------|----------------|------------|

| US 5666065A | May 22, 1996 | 1996US-0651073 |            |

INT-CL (IPC): <u>B60 Q 1/00; G01 M 19/00; G01 R 31/28</u>

ABSTRACTED-PUB-NO: US 5666065A BASIC-ABSTRACT:

An automotive supplemental inflatable <u>restraint</u> system has a firing circuit containing a squib between two <u>FETs</u> serially coupled between a voltage source and ground for effecting inflation of a <u>restraint</u>, and a deployment circuit for controlling the firing circuit. The test circuit for <u>FETs</u> comprises a regulated voltage source applied to the squib. A

detector is coupled to the firing circuit for detecting variance of the voltage on the squib beyond set thresholds above and below the regulated voltage.

The gate responds to a test signal for turning on a selected  $\underline{FET}$  so that the voltage on the squib varies beyond one of the thresholds while the selected  $\underline{FET}$  is on. The gate has a logic circuit responsive to the detector for preventing conductance of the selected  $\underline{FET}$  when the voltage breaches a threshold so that the selected  $\underline{FET}$ , if turned on, is held on for only a short period. The logic circuit has a device for producing an output signal indicative of  $\underline{FET}$  operability. If a short is present before the  $\underline{FET}$  is commanded on, a detector and the logic circuit

prevents FET conduction to avoid firing or degrading the squib.

USE/ADVANTAGE - For rapidly testing  $\underline{FETs}$  of SIR firing circuit while minimising likelihood of short occurring during testing. Also tests for shorts to battery or to ground with same circuit used for  $\underline{FET}$  tests.

ABSTRACTED-PUB-NO: US 5666065A EQUIVALENT-ABSTRACTS:

CHOSEN-DRAWING: Dwg.1/4

DERWENT-CLASS: Q16 S01 S02 T01 X22 EPI-CODES: S01-D01B5; S01-G04A1; S02-G03; S02-J02E; T01-J07C; X22-A07;

Previous Doc Next Doc Go to Doc#

## Hit List

First Hit

.

.

ъJ

Generate Collection Print Generate OACS Bkwd Refs

**Ewd Refs**

J

## Search Results - Record(s) 1 through 1 of 1 returned.

| □ 1.                         | Document ID:                                                       | <u>US 5666</u>  | <u>6065 A</u>  |                 |             |            |      |

|------------------------------|--------------------------------------------------------------------|-----------------|----------------|-----------------|-------------|------------|------|

| L17: Entr                    | y 1 of 1                                                           |                 | Fil            | e: USPT         |             | Sep 9,     | 1997 |

| US-PAT-NO: 5<br>DOCUMENT-IDE | 5666065<br>Entifier: <u>US 566606</u>                              | 5 A             |                |                 |             |            |      |

| TITLE: Fast                  | acting FET test ci                                                 | rcuit for       | SIR di         | agnostic        | s           |            |      |

| DATE-ISSUED:                 | : September 9, 1997                                                |                 |                |                 |             |            |      |

| INVENTOR-INF                 | FORMATION:                                                         |                 |                |                 |             |            |      |

| NAME                         |                                                                    | CI              | TY             | STATE           | ZIP CODE    | COUNTRY    |      |

| Ravas; Rich                  | ard Joseph                                                         | Ко              | komo           | IN              |             |            |      |

| Anderson; T                  | errell                                                             | Ca              | rmel           | IN              |             |            |      |

| Constable;                   | Robert Keith                                                       | Ko              | komo           | IN              |             |            |      |

| ASSIGNEE-INI<br>NAME         | FORMATION:                                                         | CITY            | STATE          | ZIP CODE        | e country   | TYPE CODE  |      |

| Delco Elect                  | ronics Corp.                                                       | Kokomo          | IN             |                 |             | 02         |      |

|                              | /651073 <u>[PALM]</u><br>May 22, 1996                              |                 |                |                 |             |            |      |

| INT-CL-ISSUE                 | ED: [06] <u>G01 R 31/2</u>                                         | <u>8, B60 Q</u> | <u>1/00, c</u> | <u>01 M 19/</u> | <u>00</u>   |            |      |

|                              | D: 324/769; 324/505<br>NT: <u>324/769</u> ; <u>324</u> / <u>50</u> |                 |                |                 |             |            |      |

| 340/438, 280                 | ASSIFICATION-SEARCH<br>0/735, 307/10.1<br>tion file for compl      |                 |                |                 | 505, 340/61 | , 340/436, |      |

| PRIOR-ART-DI                 | ISCLOSED:                                                          |                 |                |                 |             |            |      |

|                              |                                                                    | U.S. PA         | TENT DO        | CUMENTS         |             |            |      |

| PAT-NO                       | ISSUE-DATE                                                         | D               | ATENTEE        | -NAME           | US-0        | <u>эт.</u> |      |

| 5081442                      | January 1992                                                       |                 | to et a        |                 |             | /438       |      |

| 5166880                      | November 1992                                                      |                 | urvi           |                 |             | 424.05     |      |

| <u>3100000</u>               | HOACHINGT TAAT                                                     | <b>L</b>        | <b>AT A T</b>  |                 | 554/        |            |      |

5268643

December 1993

324/502

ART-UNIT: 223

PRIMARY-EXAMINER: Wieder; Kenneth A.

ASSISTANT-EXAMINER: Bowser; Barry C.

ATTY-AGENT-FIRM: Navarre; Mark A.

#### ABSTRACT:

The firing circuit of an inflatable restraint system is tested to verify operation of two FETs in series with a squib which are used to apply current to the squib. For the test the squib is biased to an intermediate voltage and each FET is turned on alone to apply battery or ground voltage to the squib. High and low voltage detectors sense the voltage excursion past respective thresholds to verify FET operation, and a logic circuit immediately turns off the FET to result in a very short FET on time. If a short is present before the FET is commanded on, a detector and the logic circuit prevents FET conduction to avoid firing or degrading the squib.

7 Claims, 4 Drawing figures

| Full  | Title      | Citation | Frent    | Review | Classification | Erate | Reference |          | rt allact c | Claime | []4640] | Craw C |

|-------|------------|----------|----------|--------|----------------|-------|-----------|----------|-------------|--------|---------|--------|

|       |            |          |          |        |                |       |           |          |             |        |         |        |

| Clear |            | Genera   | ite Coll | ection | Print          | F     | wd Refs   | Bky      | vd Refs     | Gener  | ate Ø   | ACS    |

|       | [ <b>r</b> |          |          |        |                |       |           | <u> </u> |             |        |         |        |

|       | Те         | rms      |          |        |                |       |           | Doc      | ument       | S      |         |        |

|       | US         | -566     | 606      | 5-A.   | did.           |       |           |          | ·           |        | 1       |        |

|       |            |          |          |        |                |       |           |          |             |        |         |        |

Display Format: TI Change Format

Go to Doc#

Previous Page Next Page

http://westbrs:9000/bin/cgi-bin/PreSearch.pl?state=fdammj.36.6&f=TOC&TOTAL\_REC=7... 5/26/06

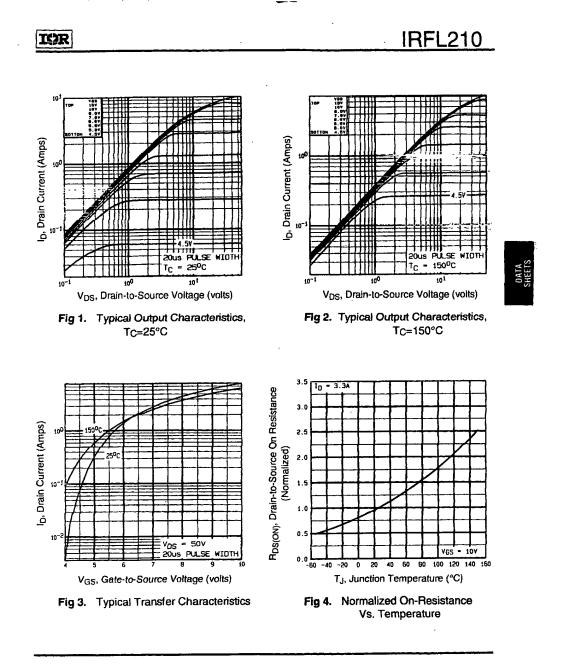

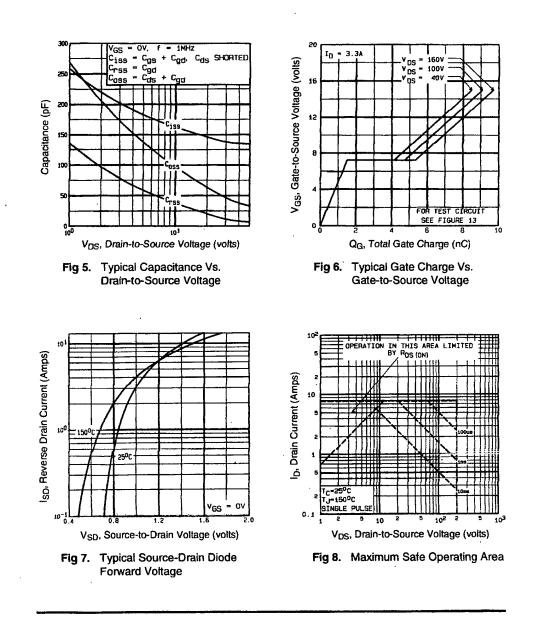

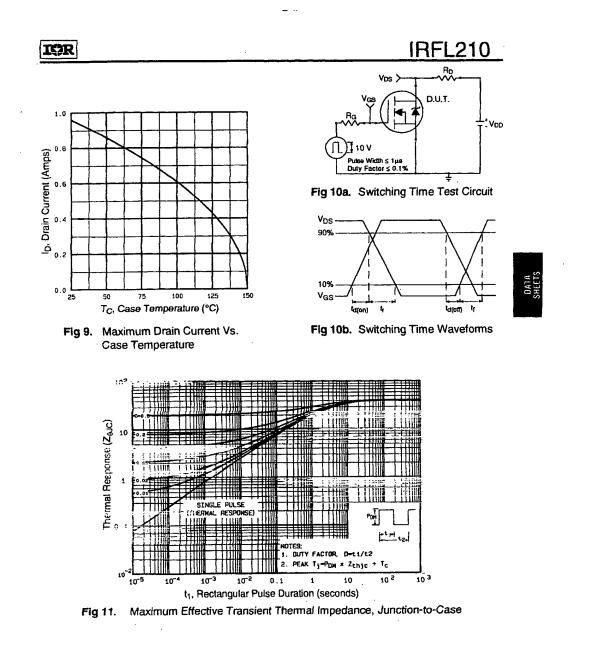

**IRFL210**

$V_{DSS} = 200V$

$R_{DS(on)} = 1.5\Omega$

l<sub>D</sub> = 0.96A

PD-9.868

## International ISR Rectifier

٠:

HEXFET<sup>®</sup> Power MOSFET

- Surface Mount

- Available in Tape & Reel

- Dynamic dv/dt Rating

- Repetitive Avalanche Rated

- Fast Switching

- Ease of Paralleling

- Simple Drive Requirements

#### Description

Third Generation HEXFETs from International Rectifier provide the designer with the best combination of fast switching, ruggedized device design, low on-resistance and cost-effectiveness.

The SOT-223 package is designed for surface-mounting using vapor phase, infra red, or wave soldering techniques. Its unique package design allows for easy automatic pick-and-place as with other SOT or SOIC packages but has the added advantage of improved thermal performance due to an enlarged tab for heatsinking. Power dissipation of greater than 1.25W is possible in a typical surface mount application.

#### Absolute Maximum Ratings

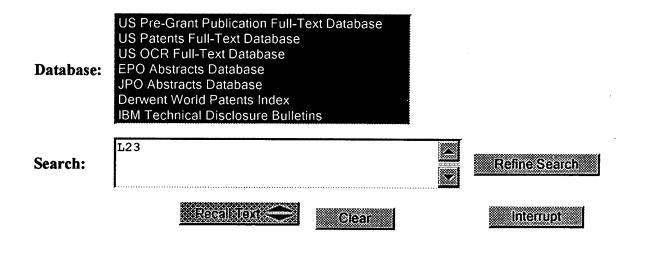

|                 | Parameter                              | Max.                  | Units |  |

|-----------------|----------------------------------------|-----------------------|-------|--|

| lp @ Tc = 25°C  | Continuous Drain Current, VGS @ 10 V   | 0.96                  |       |  |

| Ip @ Tc = 100°C | Continuous Drain Current, Vas @ 10 V   | 0.60                  | A     |  |

| Ірм             | Pulsed Drain Current ①                 | 7.7                   |       |  |

| Pp @ Tc = 25°C  | Power Dissipation                      | 3.1                   | w     |  |

| PD @ TA = 25°C  | Power Dissipation (PCB Mount)**        | 2.0                   |       |  |

|                 | Linear Derating Factor                 | 0.025                 | w^c   |  |

|                 | Linear Derating Factor (PCB Mount)**   | 0.017                 | V. 0  |  |

| V <sub>GS</sub> | Gate-to-Source Voltage                 | ±20                   | V     |  |

| EAS             | Single Pulse Avalanche Energy Ø        | 50                    | mJ    |  |

| IAR             | Avalanche Current ①                    | 0.96                  | A     |  |

| EAR             | Repetitive Avalanche Energy ①          | 0.31                  | mJ    |  |

| dv/dt           | Peak Diode Recovery dv/dt ③            | 5.0                   | V/ns  |  |

| TJ, TSTG        | Junction and Storage Temperature Range | -55 to +150           | °C    |  |

|                 | Soldering Temperature, for 10 seconds  | 300 (1.6mm from case) |       |  |

#### **Thermal Resistance**

|   |      | Parameter                         | Min. | Тур. | Max. | Units |

|---|------|-----------------------------------|------|------|------|-------|

| • | Reac | Junction-to-PCB                   | _    | —    | 40   | °C/₩  |

|   | Reja | Junction-to-Ambient (PCB mount)** | -    |      | 60   | 0.11  |

\*\* When mounted on 1" square PCB (FR-4 or G-10 Material).

For recommended footprint and soldering techniques refer to application note #AN-994.

## IRFL210

È

6

#### IØR

## Electrical Characteristics @ $T_J = 25^{\circ}C$ (unless otherwise specified)

|                 | Parameter                            | Min.    | Тур. | Max. | Units | Test Conditions                                 |

|-----------------|--------------------------------------|---------|------|------|-------|-------------------------------------------------|

| V(BRIDSS        | Drain-to-Source Breakdown Voltage    | 200     |      | _    | V     | Vgs=0V, 1p= 250µA                               |

| ΔV(BR)DSS/ΔTJ   | Breakdown Voltage Temp. Coefficient  |         | 0.30 | _    | V/°C  | Reference to 25°C, lp= 1mA                      |

| RDS(on)         | Static Drain-to-Source On-Resistance |         | -    | 1.5  | Ω     | VG5=10V, ID=0.58A ()                            |

| VGS(th)         | Gate Threshold Voltage               | 2.0     | -    | 4.0  | V     | Vos=Vgs, ID= 250µA                              |

| gts .           | Forward Transconductance             | 0.51    | —    | -    | S     | Vos=50V, Ip=0.58A ④                             |

|                 |                                      | -       | -    | 25   |       | Vps=200V, Vgs=0V                                |

| loss            | Drain-to-Source Leakage Current      | —       | —    | 250  | μA    | VDS=160V, VGS=0V, TJ=125°C                      |

|                 | Gate-to-Source Forward Leakage       | -       | -    | 100  | nA    | V <sub>GS</sub> =20V                            |

| lgss            | Gate-to-Source Reverse Leakage       | -       | —    | -100 | 1 114 | V <sub>GS</sub> =-20V                           |

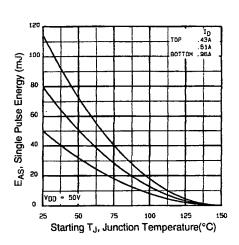

| Qg              | Total Gate Charge                    | -       | -    | 8.2  | ļ     | ID=3.3A                                         |

| Qgs             | Gate-to-Source Charge                | <b></b> | -    | 1.8  | nC    | V <sub>DS</sub> =160V                           |

| Q <sub>gd</sub> | Gate-to-Drain ("Miller") Charge      |         | —    | 4.5  |       | V <sub>GS</sub> =10V See Fig. 6 and 13 @        |

| tot(on)         | Turn-On Delay Time                   | -       | 8.2  |      | ]     | Vpp=100V                                        |

| tr              | Rise Time                            |         | 17   | —    | ns    | ID=3.3A                                         |

| td(off)         | Tum-Off Delay Time                   | -       | 14   | —    |       | R <sub>G</sub> =24Ω                             |

| tı              | Fall Time                            | -       | 8.9  | -    |       | R <sub>D</sub> =30Ω See Figure 10 ④             |

| LD              | Internal Drain Inductance            | -       | 4.0  | -    | nH    | Between lead,<br>6 mm (0.25in.)<br>from package |

| Ls              | Internal Source Inductance           |         | 6.0  | -    |       | and center of die contact                       |

| Ciss            | Input Capacitance                    | Γ       | 140  | -    |       | V <sub>GS</sub> =0V                             |

| Coss            | Output Capacitance                   |         | 53   |      | pF    | V <sub>D6</sub> = 25V                           |

| Crss            | Reverse Transfer Capacitance         | -       | 15   | -    |       | f=1.0MHz See Figure 5                           |

-

#### Source-Drain Ratings and Characteristics

|     | Parameter                                 | Min.                                                                 | Typ. | Max. | Units | Test Conditions             |

|-----|-------------------------------------------|----------------------------------------------------------------------|------|------|-------|-----------------------------|

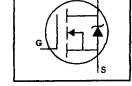

| ls  | Continuous Source Current<br>(Body Diode) | !                                                                    | -    | 0.96 | A     | MOSFET symbol showing the   |

| Ism | Pulsed Source Current<br>(Body Diode) ①   | -                                                                    | -    | 7.7  |       | p-n junction diode.         |

| Vsp | Diode Forward Voltage                     |                                                                      | - 1  | 2.0  | V .   | TJ=25°C, Is=0.96A, VGS=0V @ |

| tır | Reverse Recovery Time                     |                                                                      | 150  | 310  | ns    | T,j=25°C, I⊨=3.3A           |

| Qrr | Reverse Recovery Charge                   | -                                                                    | 0.60 | 1.4  | μC    | di/dt=100A/µs @             |

| ton | Forward Turn-On Time                      | Intrinsic turn-on time is neglegible (turn-on Is dominated by Ls+Lp) |      |      |       |                             |

#### Notes:

. . .

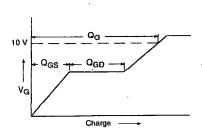

① Repetitive rating; pulse width limited by max. junction temperature (See Figure 11) ③ I<sub>SD</sub>≤3.3A, di/dt≤70A/µs, V<sub>DD</sub>≤V(BR)DSS, TJ≤150°C

② V<sub>DD</sub>=50V, starting T<sub>J</sub>=25°C, L=81mH R<sub>G</sub>=25Ω, I<sub>AS</sub>=0.96A (See Figure 12) ( Pulse width  $\leq$  300  $\mu s;$  duty cycle  $\leq\!\!2\%.$

894

.

IRFL210

896

897

...

**.** .

. .

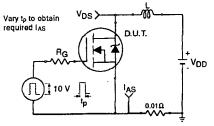

Fig 12a. Unclamped Inductive Test Circuit

Fig 12b. Unclamped Inductive Waveforms

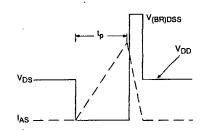

Fig 13a. Basic Gate Charge Waveform

IQR

Fig 12c. Maximum Avalanche Energy Vs. Drain Current

Fig 13b. Gate Charge Test Circuit

Appendix A: Figure 14, Peak Diode Recovery dv/dt Test Circuit – See page 1505

Appendix B: Package Outline Mechanical Drawing – See page 1508

Appendix C: Part Marking Information – See page 1516

Appendix D: Tape & Reel Information – See page 1522

898

## <u>First Hit</u> <u>Previous Doc</u> <u>Next Doc</u> <u>Go to Doc#</u>

Generate Collection Print

L5: Entry 3 of 4

File: JPAB

Apr 11, 1991

DOCUMENT-IDENTIFIER: JP 03086013 A TITLE: OVERCURRENT PROTECTIVE CIRCUIT

<u>Abstract Text</u> (2): CONSTITUTION: Gate of an N-type field effect semiconductor(FET) 1 is connected through a forward diode 3 with the drain of a P-type FET 2, the gate of which is connected through a <u>reverse diode</u> 4 with the drain of the <u>N-type FET</u> 1. Consequently, the <u>N-type FET</u> 1 and the P-type FET 2 function complementarily to interrupt overcurrent and each gate retains the gate voltage at the time of interruption. Each gate retains the gate voltage at the time of interruption for a while even if the voltage between the drains of the FETs 1, 2 drops to 0V, and the <u>N-type FET</u> 1 and the P-type FET 2 are held in interrupted state. By such arrangement, a load circuit can be protected against overcurrent.

Application Date (1): 19890830

Previous Doc

<u>Next Doc</u>

Go to Doc#

## Your wildcard search against 10000 terms has yielded the results below. Your result set for the last L# is incomplete.

The probable cause is use of unlimited truncation. Revise your search strategy to use limited truncation. Search Results -

**Search History**

DATE: Friday, May 26, 2006 Printable Copy Create Case

| <u>Set</u><br><u>Name</u><br>side by<br>side | Query                                                                                        | <u>Hit</u><br>Count | <u>Set</u><br><u>Name</u><br>result set |

|----------------------------------------------|----------------------------------------------------------------------------------------------|---------------------|-----------------------------------------|

| DB=F<br>OP=OR                                | PGPB,USPT,USOC,EPAB,JPAB,DWPI,TDBD; THES=ASSIGNEE; PLUR=YE                                   | ES;                 |                                         |

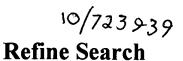

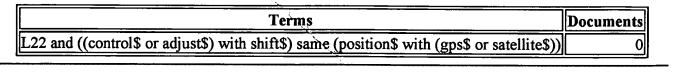

| <u>L23</u>                                   | L22 and ((control\$ or adjust\$) with shift\$) same (position\$ with (gps\$ or satellite\$)) | 0                   | <u>L23</u>                              |

| <u>L22</u>                                   | 119 or 120 or 121                                                                            | 10                  | <u>L22</u>                              |

| DB=U                                         | JSPT; THES=ASSIGNEE; PLUR=YES; OP=OR                                                         |                     |                                         |

| <u>L21</u>                                   | (5940010   6278928   5926114)![PN]                                                           | 3                   | <u>L21</u>                              |

| DB=F                                         | PGPB,USPT,USOC,EPAB,JPAB,DWPI,TDBD; THES=ASSIGNEE; PLUR=YE                                   | ES;                 |                                         |

| OP=OR                                        |                                                                                              |                     |                                         |